#### THE UNIVERSITY OF MICHIGAN

MICHIGAN SOCIETY OF FELLOWS

Rackham Building

Ann Arbor, Michigan 48109

(313) 763-1259

Richard Mandeberg

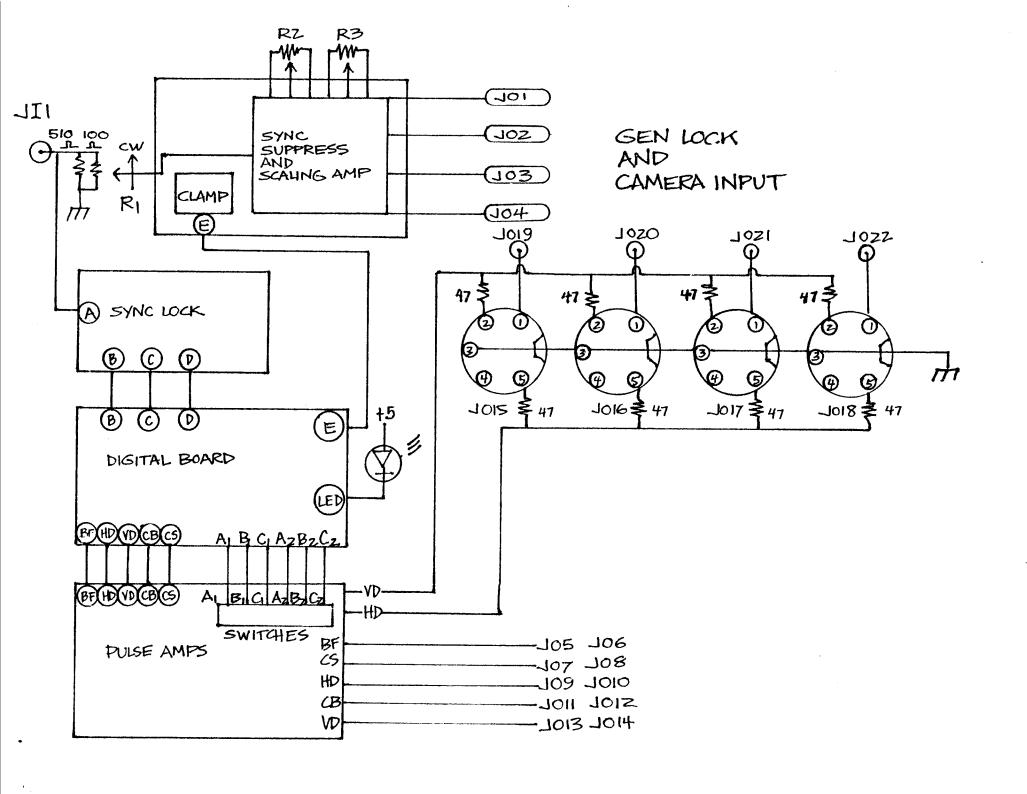

#### GEN LOCK AND CAMERA INPUT

This module locks its output pulses to an external black and white, or color video signal inputted at JIl. In addition, the signal at JIl is clamped, sync suppressed, and available at JOl - JO4. This latter process is identical to one third of the INPUT module, except that the clamp signal is generated internally (consult IP documentation for explanation).

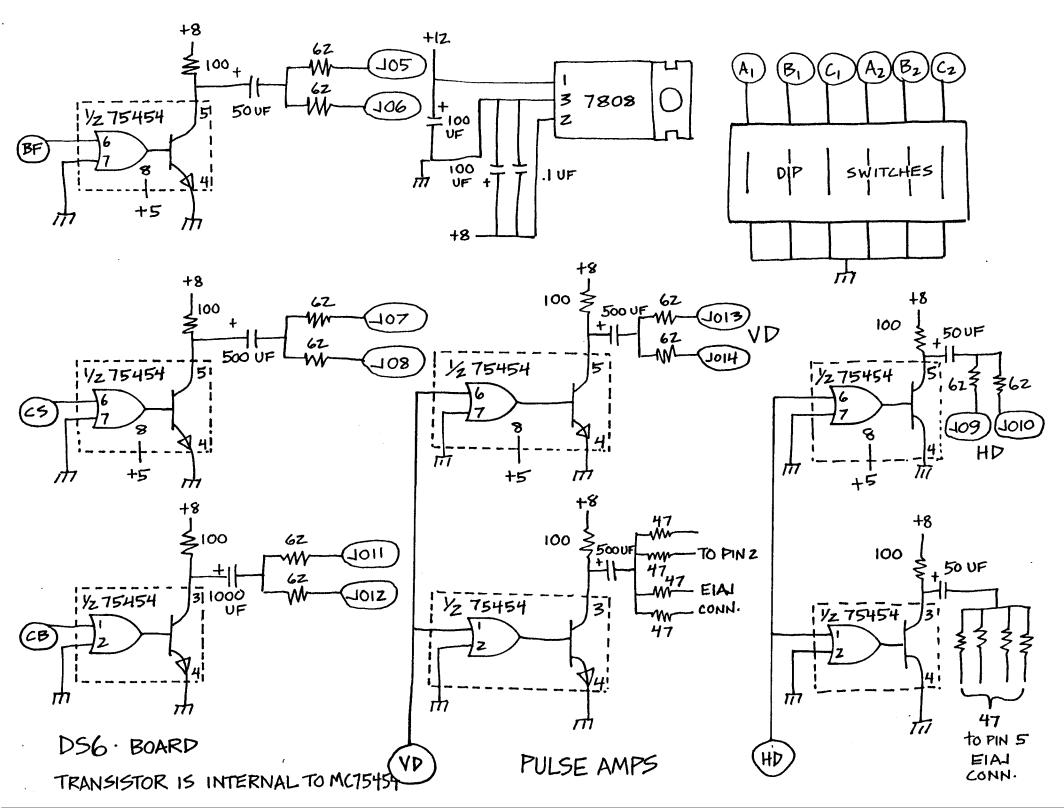

JO5 - JO14 are various synchronization and drive pulses at -4 volts into 75 ohms.

JO19 - JO22 are video signal outputs from cameras connected to the EIA-J 6 pin connectors.

The front panel LED indicates when the gen-lock is locked to an external source. Light ON means that lock is present, light OFF means the module is not locked. Outputted sync is only stable for recording when the light is ON.

#### CIRCUIT DESCRIPTION

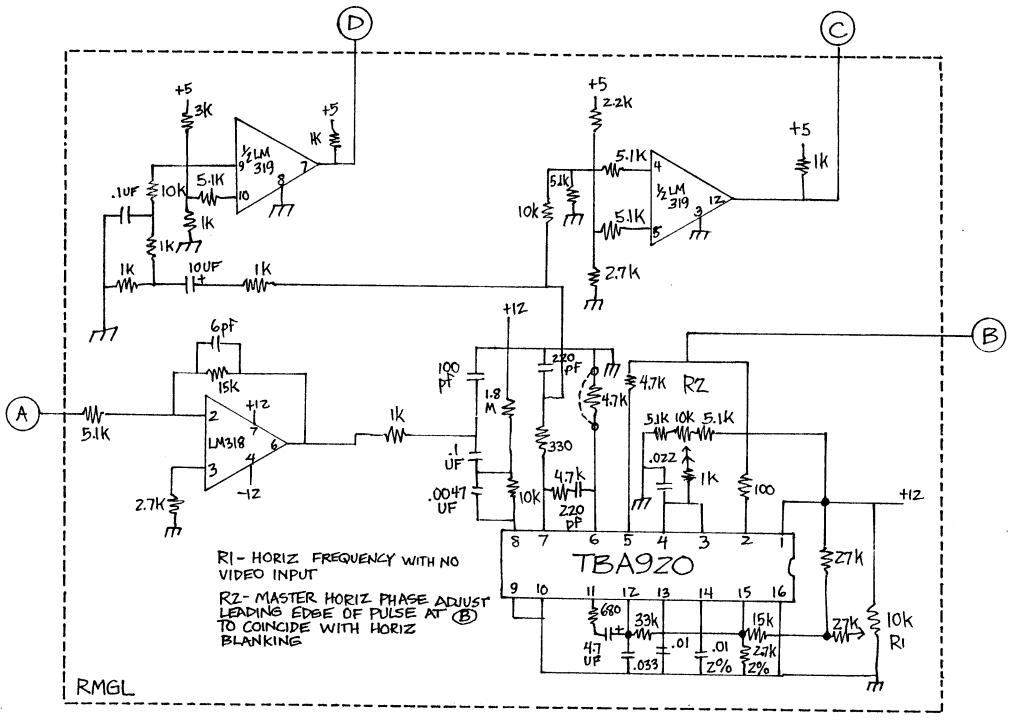

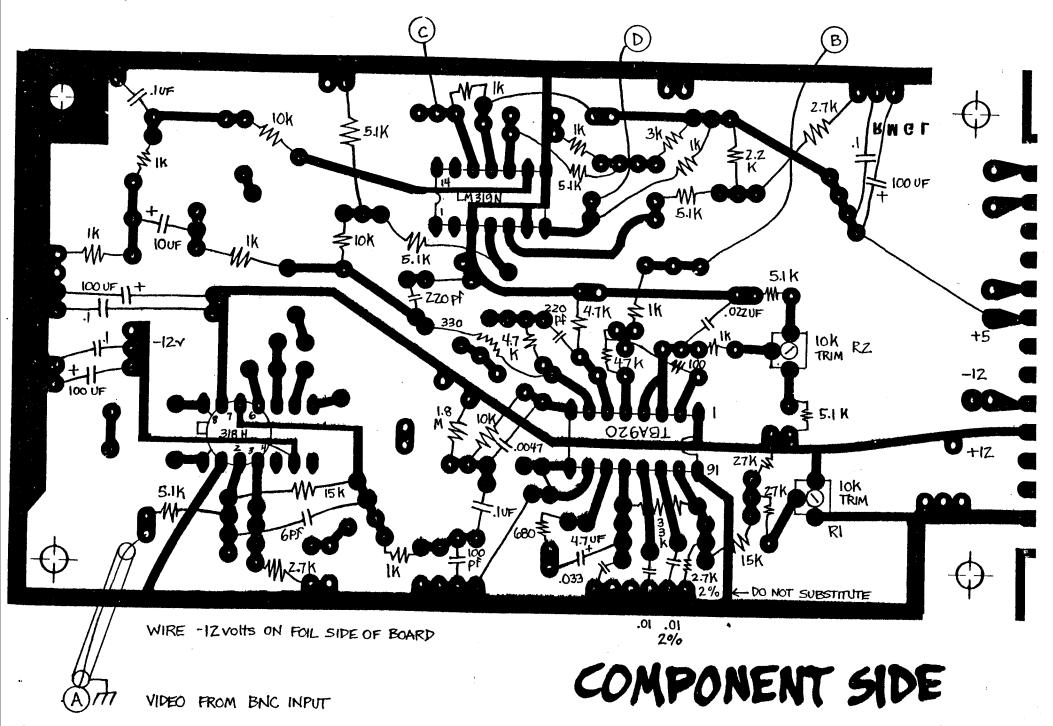

Video at JII goes to the Sync Lock board which contains a TBA920 integrated circuit. The TBA920 is a combination sync strip and horizontal phase locked loop oscillator. Stripped sync is converted to proper TTL digital voltage levels by one half of the 319 comparator. Sync is also filtered to pick off vertical. This resultant vertical trigger pulse is buffered by the other half of the 319, and used to initiate the vertical timing process on the digital board. The horizontal oscillator locks in both phase and frequency to an external video source. Rl controls the free running frequency (no video input) of the horizontal oscillator. R2 controls the phase of the oscillator when locked (video present). The leading edge of the horzontal oscillator pulse is usually set to coincide with the beginning of horizontal blanking.

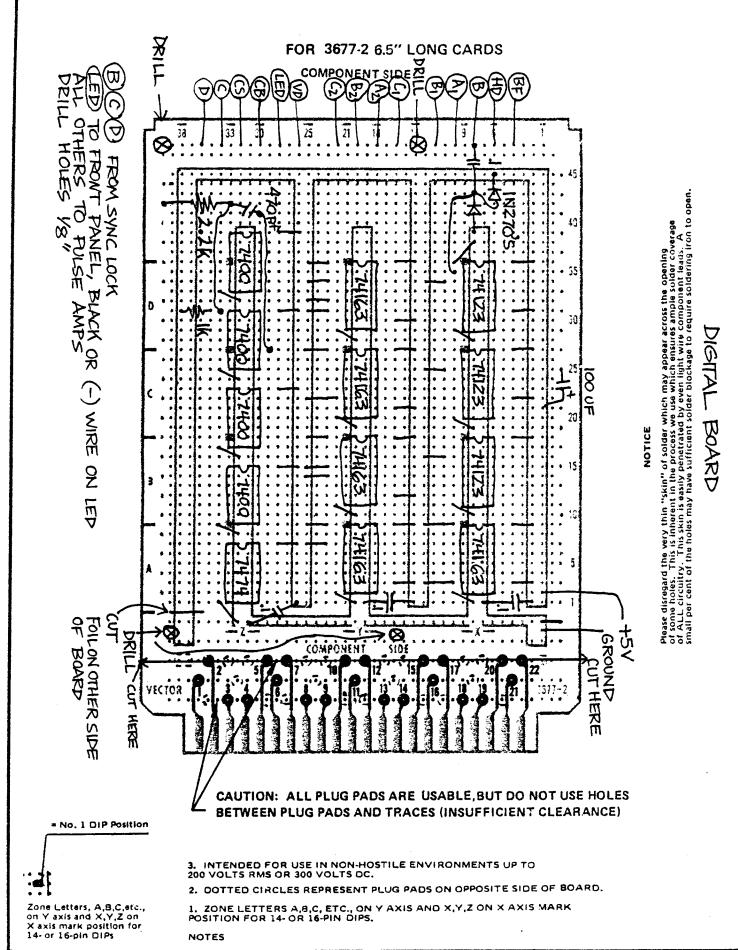

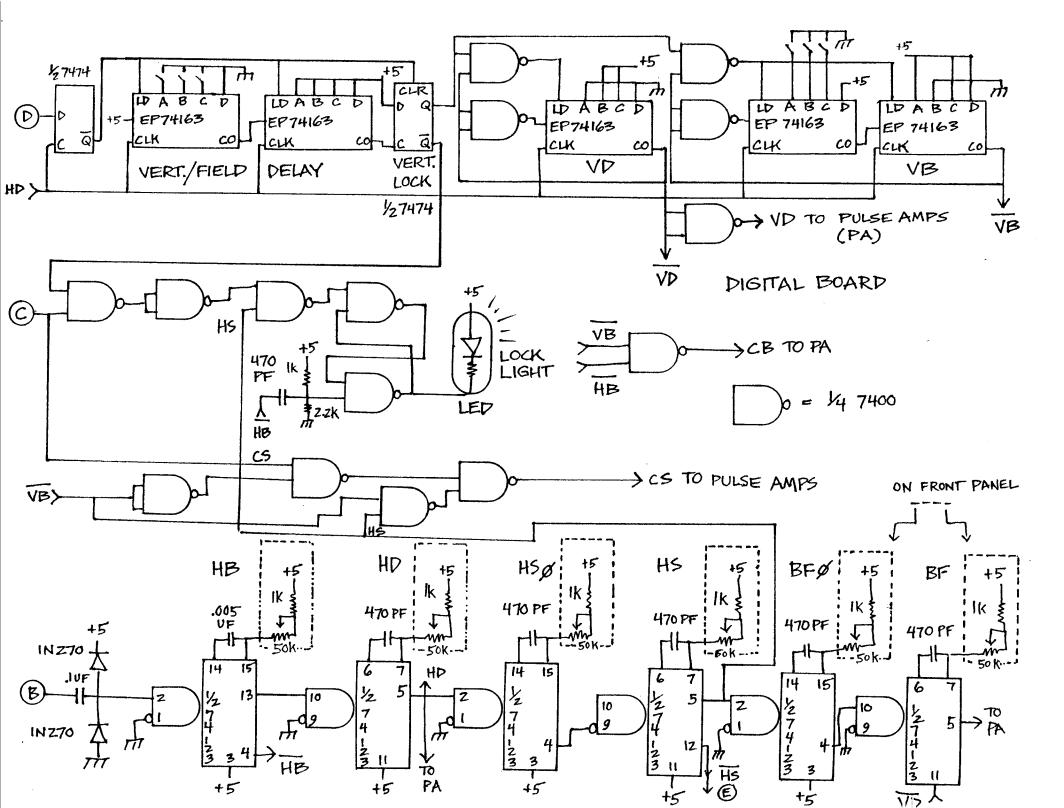

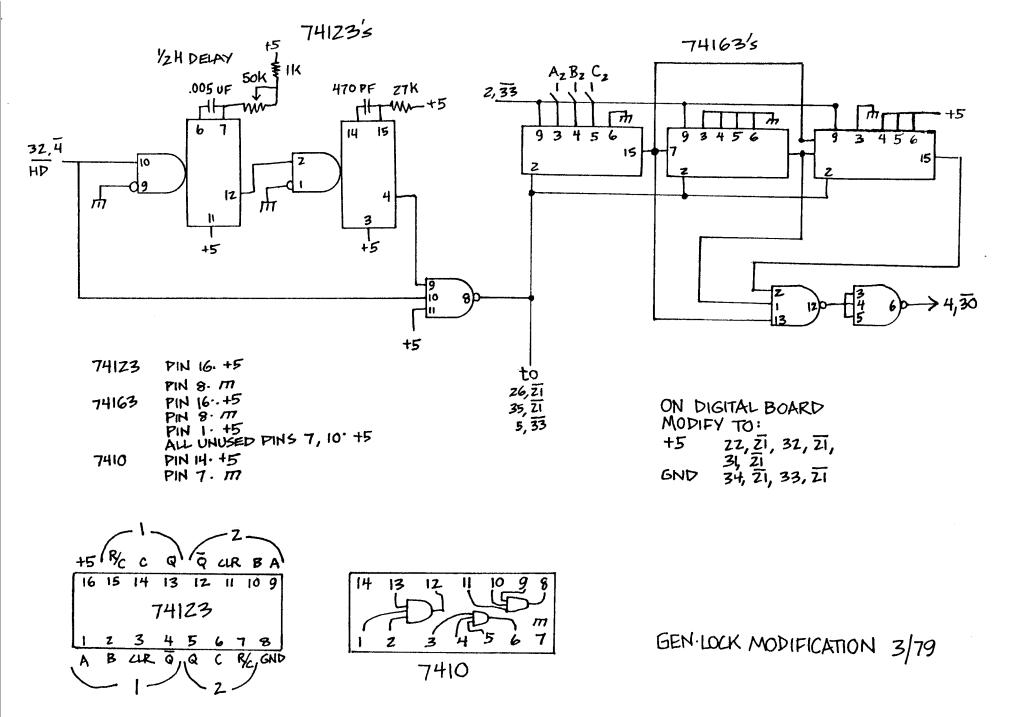

The digital board has basically three sections. The horizontal timers (74123's) are driven by the horizontal oscillator pulses. They are set up so that all pulses during the horizontal blanking interval may be retimed and rephased. The vertical section is controlled by counters (74163's) and associated NAND gates and flip-flops. DIP switches Al, Bl, Cl, control the position of vertical blanking and drive. Switches A2, B2, C2, control the length of vertical blanking. Using A2 - C2, VB may be set anywhere from 17 to 24 horizontal lines long. Other

NAND gates on the board are used for sync recombination, and to detect when the device is locked properly to an external source.

SET UP

A dual trace oscilloscope is desirable, but not absolutely necessary. One vertical channel is connected to a high quality composite video signal (like the IP). The oscilloscope must be triggered from this source, either externally, or by channel selection. Set the scope to display several lines of video.

Follow the steps in the order given. Each step must be set up correctly before continuing to the next.

- 1. Using the other vertical scope channel, attach an oscilloscope probe to line B of the sync lock board. With NO VIDEO input adjust Rl so that the horizontal oscillator rate is approximately the same as that of the video.

- 2. With a video input at JII, adjust R2 so that the phase of the horizontal oscillator pulse lines up with the beginning of horizontal blanking. This adjustment is a master horizontal phase control in that all pulses during the horizontal blaking interval are timed in relation to the leading edge of the horizontal oscillator pulse. When you change R2, all horizontal sync components will change phase accordingly.

- 3. Replace the scope probe with a 75 ohm line attached to composite blanking. Adjust RT5 for the proper length of horzontal blanking.

- 4. Looking at the output of horizontal drive, adjust RT6 for the proper length of HD.

- 5. Using the composite sync output, adjust RT3 for horizontal sync phase, and RT4 for sync length.

- 6. RT1 controls the phase position of burst flag, while RT2 controls its length. Burst flag is timed in relation to the leading edge of horizontal sync. Phase changes in sync will cause concurrent phase changes in burst flag.

- 7. Trigger the scope to display several fields of video. Using the vertical drive output, set DIP swithes Al,Bl, and Cl, to position VD at the beginning of the vertical blanking interval. The three switches have eight different possible position combinations. If VD is at best offset by one half line of video (advanced or delayed) from the beginning of vertical blanking, you are looking at the odd (B) field. In this case, set VD so that it is

advanced by one half line.

8. Attach the 75 ohm line to the composite blanking output. Vertical blanking should have the same phase as vertical drive. Adjust switches A2, B2, and C2, for the correct length of VB. 22 lines should be the maximum setting.

#### CONSTRUCTION

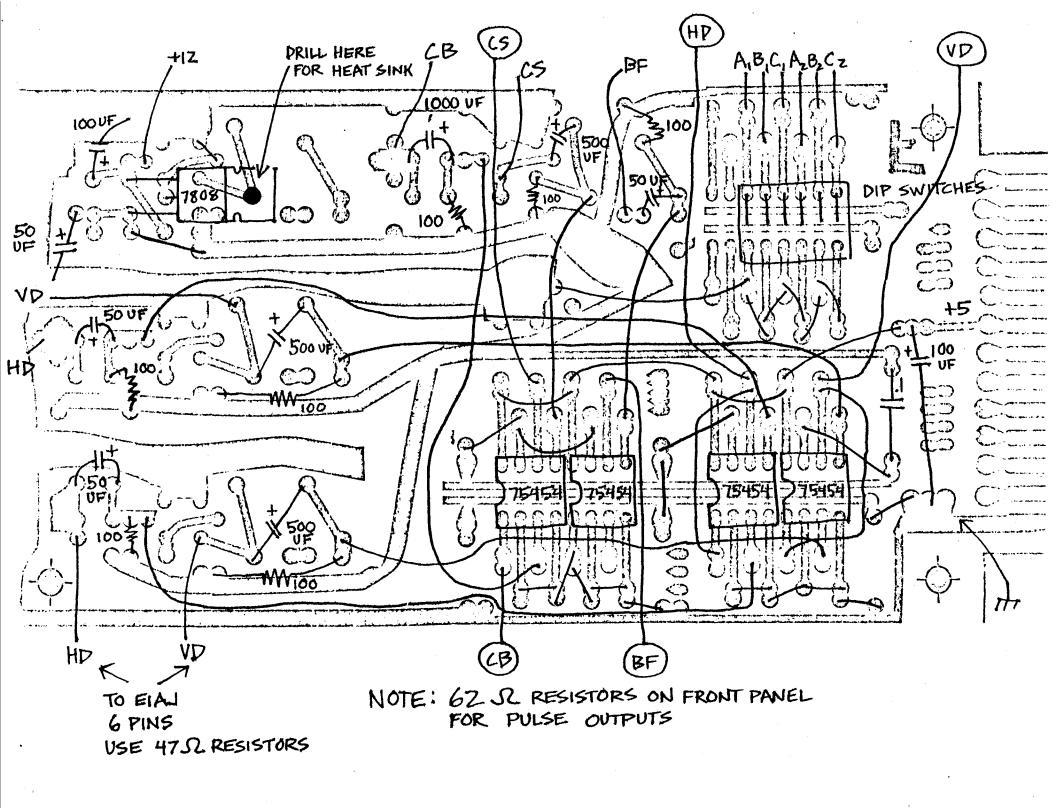

On the digital board, some wires are soldered from point to point, others are wire wrapped. Follow both the wire wrap list, and the pictorial. Remember to cut the foil, and jump ground to the outside bus, where noted.

All circuit boards, except the VS5 are mounted of 1" standoff mounting posts. VS5 is mounted at the top of the module, RMGL board in the middle, and the DS6 at the bottom. Mount the digital board behind the DS6, and RMGL boards. Input/output wires on the digital board should be kept to one edge, so that the board may be swung back for replacement of IC's, troubleshooting, etc.

Line E from the digital board runs to point JI2 on the VS5 board. Reverse the polarity of the 10uf cap. which is in series with the 470uh choke and the 1N914 diode.

On the Pulse Amp board (DS6), mount the 7808 voltage regulator to the heat sink, and then to the board itself with a 4x40 screw.

Remember to bus ground and the appropriate power to the circuit boards. +5 volts must also be run to the front panel for the LED, and the trimmers.

| RI.  | RZ-    |             | J0Z  |                              |

|------|--------|-------------|------|------------------------------|

| ηĹΙ  | R3     | 703         | 704  | FRONT FACE                   |

| LED  |        | <b>J</b> 05 | 106  | BURST FLAG                   |

|      |        | J07         | 708  | COMP SYNC                    |

| RTI  | RTZ    | 709         | 7010 | HORIZ DRIVE                  |

| RT3  | RT4    | 7011        | 7012 | COMP BLANK                   |

| RT5  | RT6    | J013        | J014 | VERT DRIVE                   |

| 7019 | J020   | J021        | J02Z | GEN LOCK AND<br>CAMERA INPUT |

| 1015 | 1016   | 1017        | 7018 |                              |

| . 5  | 8 , 18 | · .         | •    | ·                            |

÷

SYNC LOCK

# WIRING LIST FOR DIGITAL BOARD

|       | IC Placement by Pin 1                 | Capacitors on 74123's                          |

|-------|---------------------------------------|------------------------------------------------|

| IC    | Pin 1 to;                             | From Value To                                  |

| 74123 | 36, <del>9</del>                      | $35,\overline{5}$ .005 uf $34,\overline{5}$    |

| 74123 | 27, 9                                 | $31,\overline{10}$ 470 pf $30,\overline{10}$   |

| 74123 | 18, 9                                 | $26,\overline{5}$ 470 pf $25,\overline{5}$     |

| 74163 | 9, 9                                  | $22,\overline{10}$ 470 pf $21,\overline{10}$   |

| 74163 | $36,\overline{21}$                    | $17,\overline{5}$ 470 pf $16,\overline{5}$     |

| 74163 | 27, <del>21</del>                     | 13, $\overline{10}$ 470 pf 12, $\overline{10}$ |

| 74163 | $18,\overline{21}$                    |                                                |

| 74163 | 9,21                                  | Wires to Front Panel Timmers                   |

| 7400  | 39 <b>,</b> <del>33</del>             | From To                                        |

| 7400  | $31,\overline{33}$                    | 35,4 RT5 (HB)                                  |

| 7400  | 23, 33                                | 30, <del>11</del> RT6 (HD)                     |

| 7400  | 15, 33                                | $26,\overline{4}$ RT3 (HS Phase)               |

| 7474  | 7,33                                  | 21, 11 RT4 (HS)                                |

|       |                                       | $17,\overline{4}$ RT1 (BF Phase)               |

|       | Soldered Edge Wires                   | 12, 11 RT2 (BF)                                |

| Name  | Source To                             | $23,\overline{5}$ E (clamp to VS5)             |

| BF    | $47,\overline{4}$ $14,\overline{11}$  |                                                |

| HD    | 47,6 32,11                            |                                                |

| В     | $47,\overline{8}$ see pictorial       |                                                |

| Al    | 47,10 7,11                            |                                                |

| Bl    | $47,\overline{12}$ $6,\overline{11}$  |                                                |

| Cl    | $47,\overline{16}$ $5,\overline{11}$  |                                                |

| A2    | $47,\overline{18}$ $25,\overline{22}$ |                                                |

| B2    | $47,\overline{20}$ $24,\overline{22}$ |                                                |

| C2    | $47,\overline{22}$ $23,\overline{22}$ |                                                |

Soldered Edge Wires cont'd

|               |                          | <b>,</b>                   |                  |                    |

|---------------|--------------------------|----------------------------|------------------|--------------------|

| Name          | Source                   | То                         |                  |                    |

| VD            | 47,26                    | 10,35                      |                  |                    |

| LED           | 47, 28                   | 29,35                      |                  |                    |

| CB            | 47,30                    | 25, 28                     |                  |                    |

| CS            | 47,32                    | 26,35                      |                  |                    |

| С             | 47,34                    | $38,\overline{34}$         |                  |                    |

| D             | 47,36                    | 6,34                       |                  |                    |

|               | Wire Wrap                | List                       |                  |                    |

| Name          | Source                   | To                         | То               | То                 |

| Gnd           | 29 <b>,</b> <del>6</del> | 29 <b>,</b> 9              | 27 <b>,</b> 9    |                    |

| Gnđ           | 20,6                     | 20,9                       | 18,9             |                    |

| Gnd           | 11,6                     | 11,9                       |                  |                    |

| HB            | $33,\overline{6}$        | 30 <b>,</b> 6              |                  |                    |

| <del>нВ</del> | 33 <b>,</b> 9            | 27 <b>,</b> 30             |                  |                    |

| HD            | 32 <b>,</b> 9            | 26 <b>,</b> $\overline{9}$ | 8, <del></del> 9 | 8,21               |

|               |                          | $17,\overline{21}$         | 26,21            | $35,\overline{21}$ |

|               |                          | 8,21                       | 5,33             |                    |

| НSØ           | 24, 9                    | 21,6                       |                  |                    |

| HS            | 23, 9                    | 17 <b>,</b> 9              | 23, 33           | $34,\overline{30}$ |

| вғø           | 15, 9                    | 12,6                       |                  |                    |

| Gnd           | 4, 9                     | 2,9                        |                  |                    |

| +5            | $7,\overline{21}$        | 6,21                       | 5,21             | $4,\overline{21}$  |

| V Load        | 6,30                     | 2,33                       | 2,18             | 2,6                |

| +5            | 7,30                     | 7,33                       | 4,33             | $3,\overline{30}$  |

| Carry         | 8, 6                     | $3,\overline{21}$          |                  |                    |

| Carry         | 8,18                     | 4,30                       |                  |                    |

| +5            | 5,30                     | 7,30                       |                  |                    |

|               |                          |                            |                  |                    |

Wire Wrap List con'd

| Name           | Source             | To                 | То                 | То    |

|----------------|--------------------|--------------------|--------------------|-------|

| $\overline{Q}$ | 1,30               | $39,\overline{33}$ |                    |       |

| Q              | 2,30               | $10,\overline{30}$ | 18,30              |       |

| Carry          | 17, 18             | 13,6               |                    |       |

|                | 17, 18             | $11,\overline{30}$ | 13,30              | 14,30 |

|                |                    | $12,\overline{33}$ | 11,33              |       |

| Load           | 11, 18             | 9,30               |                    |       |

| EP             | $12,\overline{21}$ | 12,30              |                    |       |

| Gnd            | $16,\overline{21}$ | $13,\overline{21}$ | $11,\overline{21}$ |       |

|                | $33,\overline{21}$ | $29,\overline{21}$ |                    |       |

| Load           | 29,18              | 20,18              | 17,30              |       |

| EP             | $21,\overline{21}$ | 20,30              |                    |       |

| Carry          | 26,18              | 30,21              |                    |       |

| Carry          | 35, <del>18</del>  | 22,30              | 21,30              | 19,30 |

|                |                    | 15,33              | 14,33              |       |

|                | 22,30              | 22,33              | 26,30              |       |

| VBN            | 13,33              | $19,\overline{33}$ |                    |       |

| NAND           | 18,33              | 27,33              |                    |       |

| 11             | 28,33              | 21,33              |                    |       |

| 17             | 23,33              | 34,30              |                    |       |

| 11             | 38,33              | 20,33              |                    |       |

| 11             | 37,33              | 36,33              | $35,\overline{33}$ |       |

| 11             | 34,33              | 35,30              |                    |       |

| н :            | $33,\overline{30}$ | $30,\overline{30}$ |                    |       |

| n              | 29,30              | 29,33              |                    | ,     |

| 11             | 28,30              | 31,33              |                    |       |

| +5             | $39,\overline{30}$ | 38,30              | 37 <b>,</b> 30     |       |

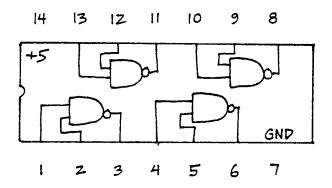

# IC'S ON DIGITAL BOARD

7400 QUAD NAND

14 13 12 11 10 9 8

+5 ZCLR ZD ZCK ZPR ZQ ZQ

CLR 1D 1CK 1PR 1Q 1Q GND

1 2 3 4 5 6 7

7474

DUAL D TYPE FLIP FLOP

16 15 14 13 12 11 10 9

+5 CO QA QB QC QD ET LD

CLR CLK A DATA IN D EP GND

1 Z 3 4 5 6 7 8

74163

4-BIT COUNTER

## THE UNIVERSITY OF MICHIGAN

Michigan Society of Fellows

Rackham Building

Ann Arbor, Michigan 48109

(313) 763-1259

Richard Mandeberg

#### ADDENDUM TO THE GEN LOCK

In its initial design, the Gen Lock misplaces the leading edge of vertical blanking by one half line during the odd field. This circuit addition will fix that problem, and reestablish proper interlace to composite blanking. Vertical sync information is unchanged by this addition, as sync was already correctly interlaced in the previous design.

This addendum is useful to people who anticipate that much of their work will be time base corrected, or that they will be working often in a broadcast environment. The earlier design will work fine with all non-broadcast equipment, and its use does not preclude the ability to time base correct your videotapes.

NOTE: The addition of this circuit makes the construction of the Gen Lock more complex and difficult. If you don't understand how to put it in, use the original design. The module will work fine, and you can add the additional circuit later.

#### CONSTRUCTION

Build the circuit on perf board, wire wrapping the connections. Mount it above the digital board. Remember to bus ground and +5 volts to the board, and bypass +5 to ground with a .luf cap. every few IC's. Mount the 74123 and the 50k trimmer near the rear of board, with the trimmer adjust facing back. Drill a hole in the back panel in the appropriate place for the 1/2 H adjustment. On the main digital board remove the 74163 which is in line with the 74123's, and remove the 74163 below it also. Do not wire wrap wires associated with these two IC's.

### SET UP

Attach an oscilloscope probe to pin 8 of the 7410. Display it, and a high quality video signal (also inputted to the Gen Lock) on both channels of the scope. Trigger the scope to show the beginning of the vertical blanking interval, including equalization pulses and sync. Adjusting the 50k trimmer will change the phase of the 1/2 line pulse. Using every other equalization pulse as a guide, adjust these pulses so that their leading edge is coincident, or slightly ahead of the leading edge of the equalization pulses.

# PARTS LIST

NOTE: Only parts which are not normally used in the IP are listed. All others are standard IP parts.

## Newark

| 1<br>1<br>1<br>1<br>1<br>1<br>1 | 13F148<br>12F9615<br>17F2202<br>38F1368<br>38F1362 | DC-1/4 2.7k<br>3068-P-50k<br>715P10354JD3<br>3677-2<br>K32<br>P184A<br>P185<br>W28-6A<br>W28-6B<br>W28-6E<br>W28-6F | 2.74k ohm 1% 50k trimmer .0luf 5% Vector Board J Pins for wire wrap Vector Wire Wrap Tip Vector Wire Wrap Adapter Vector Wire """""""""""""""""""""""""""""""""""" |

|---------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8<br>14<br>1<br>1               | 57F1775<br>57F1776<br>58F156<br>57F2910            | C91-14-00<br>C91-16-00<br>29136ABH<br>76B06<br>559-0102-002                                                         | 14 Pin Wire Wrap Socket<br>16 Pin Wire Wrap Socket<br>Heat Sink<br>SPST 6 Rockers<br>Dialight Red LED w/ internal<br>resistor                                      |

# SEMICONDUCTOR SPECIALISTS OR HAMILTON AVNET

| 1 | TBA920    | Horizontal Oscillator | Fairchild |

|---|-----------|-----------------------|-----------|

| 1 | uA7808UC  | +8 Volt Regulator     | Fairchild |

| 1 | LM319N    | Comparator            | National  |

| 4 | MC75454P  | Peripheral Driver     | Motorola  |

| 1 | LM318H    | Op Amp                | National  |

| 2 | CA3030    | Op Amp                | RCA       |

| 4 | DM74123N  | Mono Multi            | National  |

| 6 | DM74163AN | 4 Bit Counter         | <b>F9</b> |

| 1 | DM7474N   | Flip Flop             | 11        |

| 1 | DM7410N   | Triple In NAND        | **        |

| 4 | DM7400N   | Quad NAND             | 11        |

## ECI

| 1 | VS5  |

|---|------|

| 1 | DS6  |

| 1 | RMGL |